# White Paper 2: A Case for Lowering Component-level CDM ESD Specifications and Requirements

# **Industry Council on ESD Target Levels**

# May 2021

Revision 3.0

### Abstract

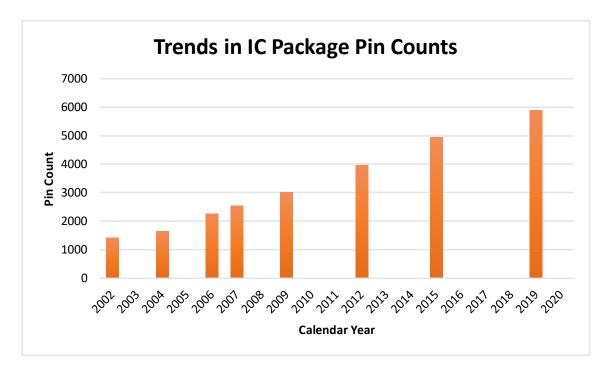

CDM has become the primary real-world ESD event metric describing ESD charging and rapid discharge events in automated handling, manufacturing, and assembly of IC devices. Its importance has dramatically increased over the years as package feature sizes, capacitance, and pin count have scaled upward. In years past, arbitrary CDM protection levels had been specified as IC qualification goals with little background information available on actual/realistic CDM event levels and the protection methods available in manufacturing controls and device design for the safe production of IC components. The rapid advancement of IC technology scaling, coupled with the increased demand for high-speed circuit performance, made it increasingly difficult to guarantee a customer-specified "500 volts" CDM specification and as this update will discuss, even 250 volts can create challenges. At the same time, the required static control methods available for production area CDM protection at each process step have not been fully outlined. Therefore, a realistic CDM specification target must be defined in terms of available and commonly practiced CDM control methods and must reflect current ESD design constraints. Additionally, as technology scaling continues, very high-speed I/Os are being introduced which demand the need for lower CDM target levels in order to achieve the needed I/O performance. This is the scope of this latest update to White Paper 2.

By balancing improved static ESD controls specific to CDM, and limited ESD design capability in today's leading technologies, we recommend a CDM specification target level of 250 volts with consideration for lower CDM target levels in unique cases where very high-speed I/O performance is needed. These target levels are a realistic and safe CDM level for manufacturing and handling today's products using basic CDM control methods, or advanced CDM control techniques as needed based on the target level.

At the same time, we show that the current trend of silicon technology scaling will continue to place further restrictions on achievable CDM levels. It is, therefore, necessary that the Industry Council presents a realistic CDM roadmap for consideration by the industry moving forward to 7 nm technologies and beyond, including 2.5D and 3D technologies.

# About the Industry Council on ESD Target Levels

The Council was initiated in 2006 after several major U.S., European, and Asian semiconductor companies joined to determine and recommend ESD target levels. The goal was to set ESD requirements on IC products for safe handling and mounting in ESD protected areas while addressing the constraints from silicon technology scaling and IC design. The Council now consists of representatives from active full member companies and numerous associate members from various support companies.

| Core Members                                                             | Core Members                                               |

|--------------------------------------------------------------------------|------------------------------------------------------------|

| Robert Ashton, Minotaur Labs                                             | Guido Notermans, Retired                                   |

| Andrea Boroni, STMicroelectronics                                        | Motostugu Okushima, Renesas                                |

| Ashok Alagappan, Ansys                                                   | Nate Peachey, Qorvo                                        |

| Brett Carn, Intel Corporation                                            | David Pommereneke, Graz University of Technology           |

| Ann Concannon, Texas Instruments                                         | Alan Righter, Analog Devices                               |

| Jeff Dunnihoo, Pragma Design                                             | Theo Smedes, NXP Semiconductors                            |

| Charvaka Duvvury, iT2 Technologies (Chairman)                            |                                                            |

| <u>cduvvury@gmail.com</u>                                                | Andrew Spray, Synaptics                                    |

| David Eppes, AMD                                                         | Mark Styduhar, Marvell                                     |

| Harald Gossner, Intel Corporation (Chairman)<br>harald.gossner@intel.com | Teruo Suzuki, Socionext                                    |

| Reinhold Gärtner, Infineon Technologies                                  | Pasi Tamminen, EDR & Medeso                                |

| Robert Gauthier, Globalfoundries                                         | Scott Ward, Texas Instruments                              |

| Steffen Holland, Nexperia                                                | Terry Welsher, Dangelmayer Associates                      |

| Masamitsu Honda, Impulse Physics Laboratory                              | Joost Willemen, Infineon Technologies                      |

| Stevan Hunter, Retired                                                   | Heinrich Wolf, Fraunhofer EMFT                             |

| Hiroyasu Ishizuka, Maxwell                                               | Mike Wu, TSMC                                              |

| Nathan Jack, Intel Corporation                                           | Benjamin Van Camp, Sofics                                  |

| Peter de Jong, Synopsys                                                  |                                                            |

| Chanhee Jeon, Samsung                                                    | Contributing Authors JEP 157 release 2009 and release 2020 |

| Reza Jalilizeinali, Qualcomm                                             | Wolfgang Stadler, Intel Corporation (release 2020)         |

| John Kinnear, IBM                                                        | Stephen Beebe, AMD (release 2009)                          |

| Hans Kunz, Texas Instruments                                             | Melanie Etherton, Freescale Semiconductor (release 2009)   |

| David Klein, PSemi                                                       | Yasuhiro Fukuda, OKI Engineering (release 2009)            |

| Peter Koeppen, ESD Unlimited                                             | Ron Gibson, Celestica (release 2009)                       |

| Tim Maloney, Intel Corporation (retired)                                 | Satoshi Isofuku, Tokyo Electronics Trading (release 2009)  |

| Tom Meuse, Thermo Fisher Scientific                                      | Larry Johnson, Avagotech (release 2009)                    |

| Mujahid Muhammad, Globalfoundries                                        | James Miller, Freescale Semiconductor (release 2009)       |

|                                                                          |                                                            |

| Associate Members                                      | Associate Members                  |

|--------------------------------------------------------|------------------------------------|

| Arnold Steinman, SimcoIon                              | Kai Esmark, Infineon               |

| Bernard Chin, Qorvo                                    | KH Lin, Amazing IC                 |

| Brian Langley, Oracle                                  | Kitae Lee, Samsung                 |

| Changsu Kim, Samsung                                   | Larry Johnson, Avagotech           |

| Che Hao, Amazing IC                                    | Marcus Koh, Everfeed               |

| C Hillman, Ansys                                       | Marty Johnson, Retired             |

| Christian Russ, Infineon                               | Mike Chaine, Micron                |

| CJ Chao, Richwave                                      | Ming-Dou Ker, NCTU                 |

| Dave Swenson, Affinity Static Control Consulting, Inc. | Melissa Jolliff, Aero              |

| Efraim Aharon, Towersemi                               | Markus Mergens, QPX                |

| Fred Bahrenburg, Dell                                  | M Lee, Semtech                     |

| Frederic Lafon, Valeo                                  | Morphy Gao, Hisilicon              |

| Gery Pettit, Retired                                   | MyoungJu.Yun, Amkor                |

| Gaurav Singh, Dialog Semiconductors                    | Natalie Hernandez, Ansys           |

| Graver Chang, ma-tek                                   | Nobuyuki Wakai, Toshiba            |

| Greg O'Sullivan, Micron                                | Philip Baltar, Renesas             |

| Hangu Kim, Samsung                                     | Ramon Del Carmen, Amkor            |

| Mike Heaney, Amazon                                    | Rick Wong, Retired                 |

| Henning Lohmeyer, Bosch                                | Rita Fung, Cisco                   |

| Hans Kunz, Texas Instruments                           | Ron Peirce, Simco                  |

| Horst Gieser, Fraunhofer EMFT                          | Rich Webber, Qualcomm              |

| Howard Gan, SMICS                                      | Ryan, Amazing IC                   |

| Isabel Stumfall, Semtech                               | Soonjae Kwon, Samsung              |

| Jaehyok Ko, Samsung                                    | Sreeker Dundigal, Qualcomm         |

| Jonathan Brodsky, Texas Instruments                    | Ted Dangelmayer, Dangelmayer Ass.  |

| Jim Colby, Littelfuse                                  | Tom Diep, Texas Instruments        |

| Jeremy Smallwood, Electrostatics                       | Vrashank Shukla, Texas Instruments |

| Jon Williamson, Renesas                                | Wenyi Chen Qualcomm                |

| Joshua Yoo, Core Insight,                              | Xiong Ying, Huawei                 |

| James Winstead, Qualcomm                               | Younchul Oh, Samsung               |

|                                                        |                                    |

|                                                        |                                    |

|                                                        |                                    |

### **Mission Statement**

The mission of the Industry Council on ESD Target Levels is to review the ESD robustness requirements of modern IC products to allow safe handling and mounting in an ESD protected area. While accommodating both the capability of the manufacturing sites and the constraints posed by the downscaled process technologies on practical protection designs, the Council will provide a consolidated recommendation for the future ESD target levels. The Council Members and Associates will promote these recommended targets for adoption as company goals. Being an independent institution, the Council will present the results and supportive data to all interested standardization bodies.

### Preface

This document was written with the intent to provide information for quality organizations in both semiconductor companies and their customers to assess and make decisions on safe ESD CDM level requirements. We will show through this document why a more realistic definition of the ESD CDM target levels for components is not only essential but is also urgent. The document is organized in different chapters with additional information in the appendices to give as many technical details as possible to support the purpose given in the abstract. We begin the paper with an Executive Summary and chapter/appendix highlights followed by frequently asked questions (FAQ) so that the reader can readily find critical information without having to scan through the whole document. Additionally, these FAQs are intended to avoid any misconceptions that commonly occur while interpreting the data and the conclusions herein. All component-level ESD testing specified within this document adheres to the methods defined in the appropriate ANSI/ESDA/JEDEC or JEITA specifications.

### **Disclaimers**

The Industry Council on ESD Target Levels is not affiliated with any standardization body and is not a working group sponsored by JEDEC, ESDA, JEITA, IEC, or AEC.

This document was compiled by recognized ESD experts from numerous semiconductor supplier companies and contract manufacturers. The data represents CDM and field failure information collected from a large variety and volume of IC products; no specific components are identified. The readers should not construe this information as evidence for unrelated field failures resulting from electrical overstress events or system-level ESD incidents. The document only refers to component-level ESD recommendations which should have no impact on system-level ESD requirements.

The Industry Council, while providing these recommendations, does not assume any liability or obligations for parties who do not follow proper ESD control measures.

# **Glossary of Terms**

| AEC          | Automotive Electronics Council                                      |

|--------------|---------------------------------------------------------------------|

| BGA          | ball grid array                                                     |

| CBE          | charged board event                                                 |

| CBM          | charged board model                                                 |

| CCD          | charged coupled device                                              |

| CC-TLP       | capacitively-coupled transmission line pulse                        |

| CDM          | charged device model                                                |

| CMOS         | complementary metal-oxide semiconductor                             |

| СРМ          | charge plate monitor                                                |

| DC           | direct current                                                      |

| DDR          | double data rate                                                    |

| DIP          | dual-in-line package                                                |

| DPM          | defects per million                                                 |

| DRAM         | dynamic random-access memory                                        |

| DSP          | digital signal processor                                            |

| DUT          | device under test                                                   |

| EMC          | electromagnetic compatibility                                       |

| EMI          | electromagnetic interference                                        |

| EOS          | electrical overstress                                               |

| EPA          | ESD protected area                                                  |

| ESD          | electrostatic discharge                                             |

| ESDA         | Electrostatic Discharge Association; ESD Association; EOS/ESD       |

|              | Association                                                         |

| ESDS         | electrostatic discharge sensitive                                   |

| ESVM         | electrostatic voltmeter                                             |

| FA           | failure analysis                                                    |

| FAR          | failure analysis report                                             |

| FAQ          | frequently asked question                                           |

| FCDM (FICDM) | field-induced charged device model                                  |

| FIM          | field-induced model                                                 |

| FinFET       | Fin field-effect transistor                                         |

| FWHM         | full width at half maximum                                          |

| GND          | ground, negative voltage supply                                     |

| GPIO         | general purpose I/O                                                 |

| GSA          | Global Semiconductor Alliance                                       |

| HBM          | human body model                                                    |

| HDMI         | high-definition multimedia interface                                |

| HSS (HSSL)   | high-speed serial link                                              |

| IC           | integrated circuit                                                  |

| ICT          | in-circuit test                                                     |

| IP           | intellectual property                                               |

| I/O          | input/output                                                        |

| IEC          | International Electrotechnical Commission                           |

| JEDEC        | JEDEC Solid State Technology Association                            |

| JEITA        | Japan Electronics and Information Technology Industries Association |

| LGA          | land grid array                                                     |

| LICCDM       | low-impedance contact charged device model                          |

| LNA       | low noise amplifier                                                            |

|-----------|--------------------------------------------------------------------------------|

| LV        | low voltage                                                                    |

| MCM       | multichip module                                                               |

| MIPI      | mobile industry processor interface                                            |

| MM        | machine model                                                                  |

| MV        | medium voltage                                                                 |

| NFET      | N-type field-effect transistor                                                 |

| NMOS      | N-channel metal-oxide-semiconductor                                            |

| NPN       | negative-positive-negative (transistor)                                        |

| PAM       | pulse-amplitude modulation                                                     |

| PCB       | printed circuit board                                                          |

| РСТА      | process capability and transition analysis                                     |

| PFET      | P-type field-effect transistor                                                 |

| PMOS      | P-channel metal-oxide-semiconductor                                            |

| QFP       | quad flat pack                                                                 |

| RC        | resistor-capacitor network                                                     |

| RLC (LRC) | resistor-inductor-capacitor network                                            |

| RLDRAM    | reduced latency DRAM                                                           |

| RF        | radio frequency                                                                |

| SATA      | serial advanced technology attachment                                          |

| SBLK      | silicide blocked                                                               |

| SCR       | silicon-controlled rectifier                                                   |

| SDM       | socketed device model                                                          |

| SERDES    | serializer/deserializer transceiver that converts parallel data to serial data |

| SMT       | surface mount technology                                                       |

| SoC       | system-on-chip                                                                 |

| TIVA      | thermally induced voltage alteration                                           |

| TLP       | transmission line pulse                                                        |

| TQFP      | thin quad flat pack                                                            |

| USB       | universal serial bus                                                           |

| ULSI      | ultra-large-scale integration                                                  |

| VDD       | positive voltage supply                                                        |

| Vds       | drain/source voltage                                                           |

| VF-TLP    | very fast transmission line pulse                                              |

| VSS       | negative voltage supply                                                        |

| WCDM      | wafer-level charged-device model                                               |

| WSP       | wafer-scale package                                                            |

| ZIF       | zero insertion force                                                           |

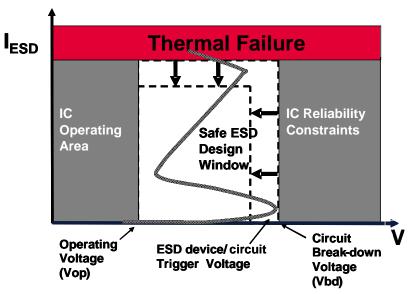

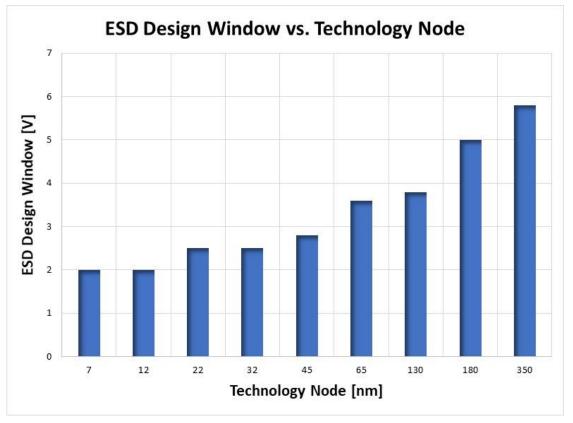

ESD Design Window: The ESD protection design space for meeting a specific ESD target level while maintaining the required I/O performance parameters (such as leakage, capacitance, noise, etc.) at each subsequent technology node.

ESD robustness: The capability of a device to withstand the required ESD-specification tests and still be fully functional.

$I_{t2}$ : The current point where a transistor enters its second breakdown region under ESD pulse conditions, and it is irreversibly damaged.

Node: Within a circuit, a point of interconnection between two or more components.

## **Executive Summary**

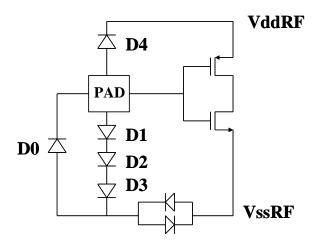

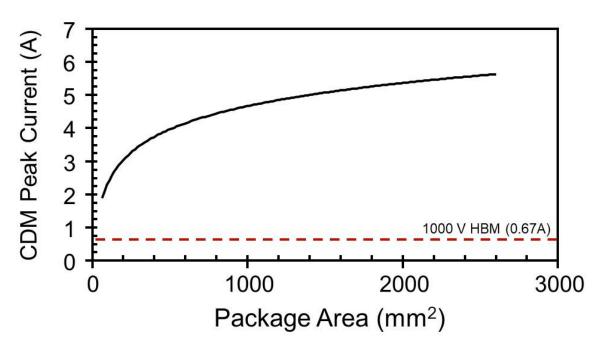

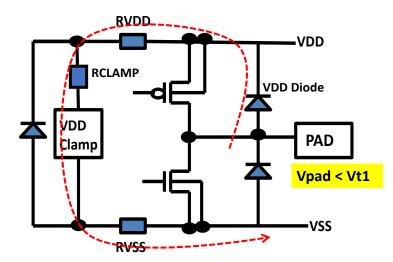

It is well understood in the IC industry that the charged device model (CDM) is the ESD model that best describes real-world component-level ESD events during IC manufacturing and handling. See Chapter 1 for details. In contrast to HBM, where basic ESD control measures in manufacturing ensure a safe and realistic specification level (i.e. 1000 volts HBM as reported in White Paper I [1]), CDM protection requires these basic ESD controls as well as additional ESD controls such as managing against the charging of insulators, at specific process steps, to ensure safe and realistic levels for all product designs below 200 volts. Some of these additional process assessment techniques that may need to be involved are detailed out in a recently released standard practice from the ESDA entitled "Protection of Electrostatic Discharge Susceptible Items - Process Assessment Techniques", ANSI/ESD SP17.1. As IC applications have moved towards ultra-highspeed I/O interfaces (> 200 Gb/s) over the last decade, this CDM threat has been further exacerbated in terms of qualification levels to achieve design performance. This has driven the need for advanced control methods to be implemented for safe manufacturing in the production area. Combined with these new developments the sensitivity and accuracy for CDM testing have become more critical than ever. This update to White Paper 2 addresses the current requirements for CDM presenting a holistic view of the CDM roadmap including both standard and advanced high-speed products.

Some important aspects of the CDM challenge must be understood:

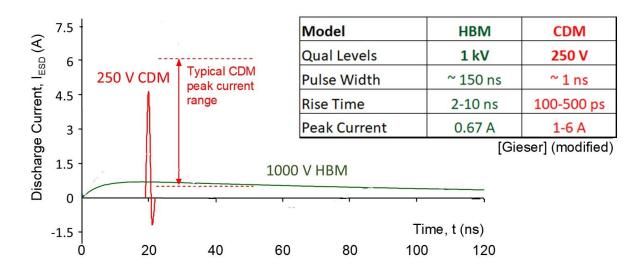

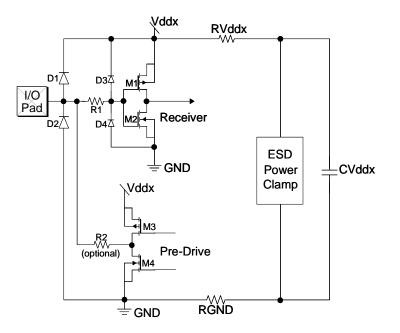

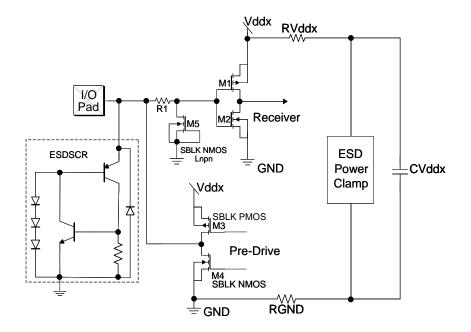

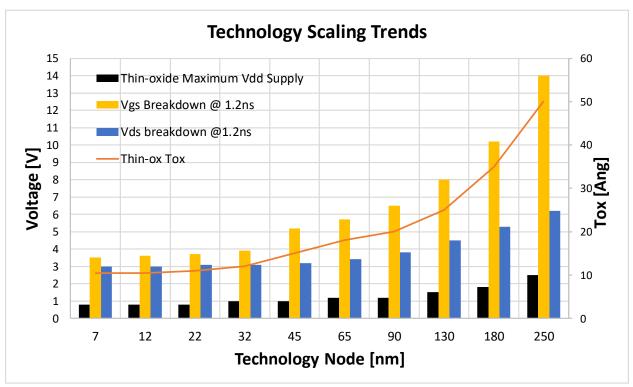

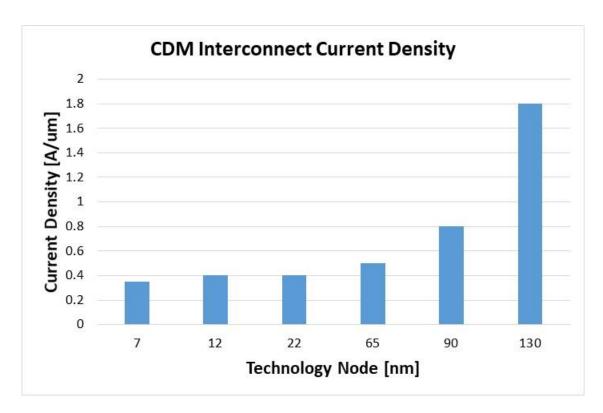

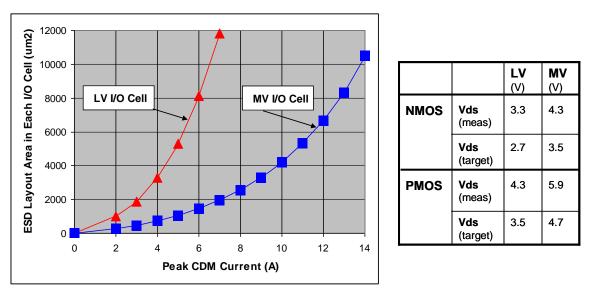

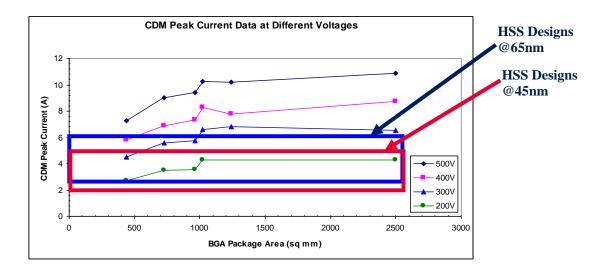

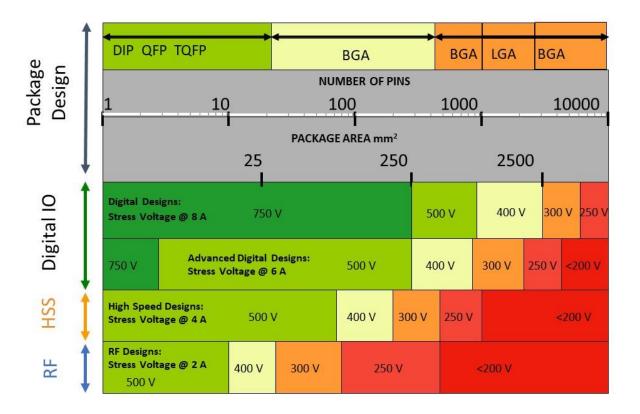

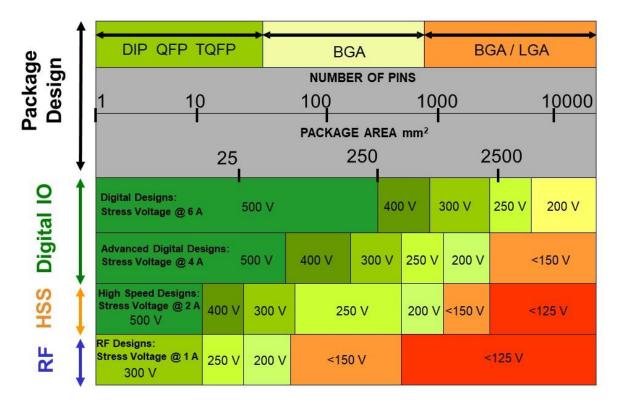

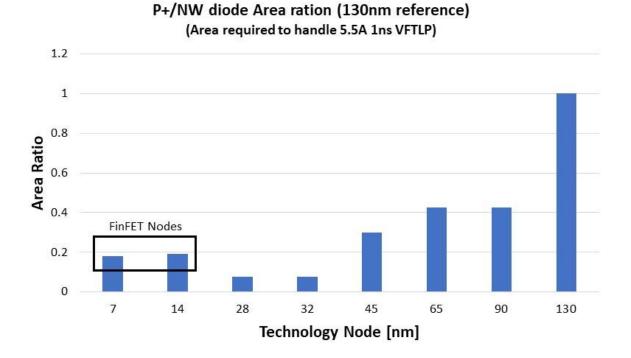

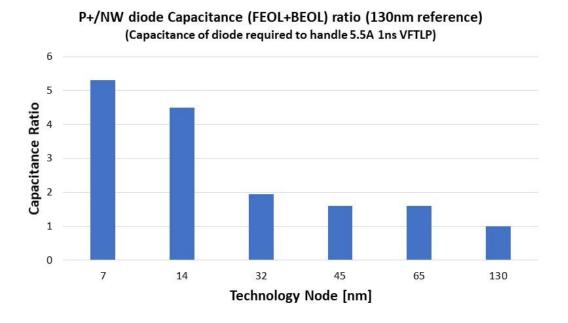

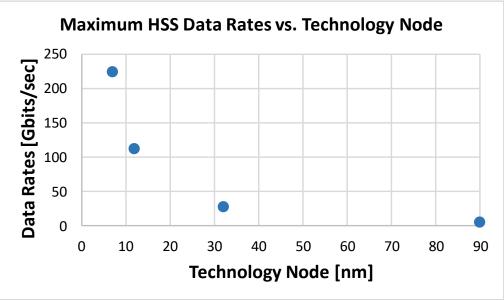

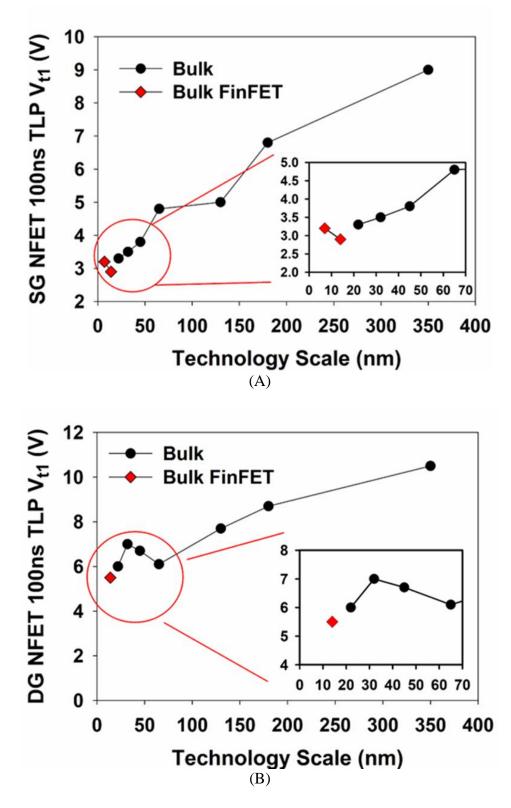

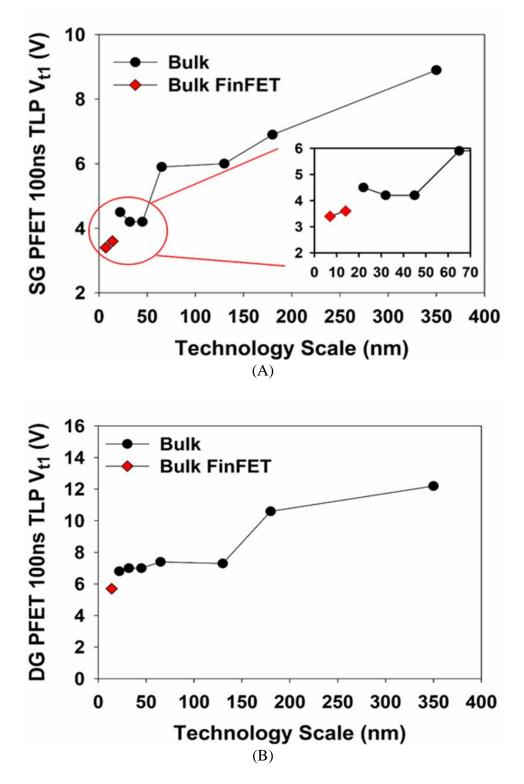

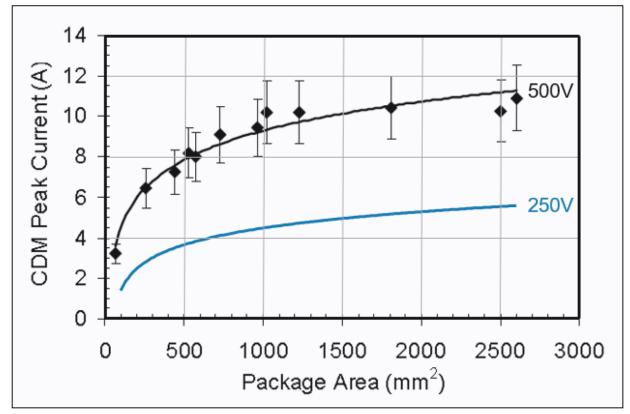

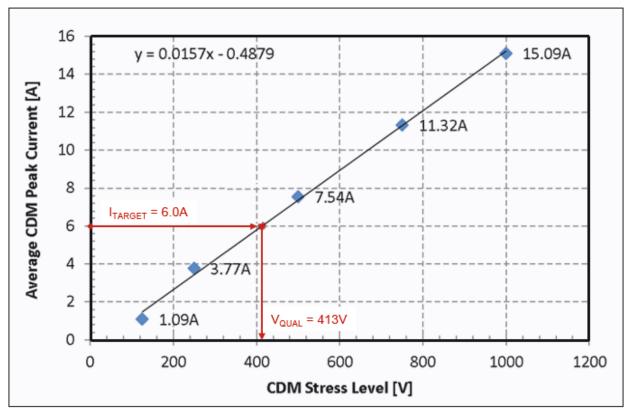

IC Design / Development Constraints: Constraints from silicon technology scaling, IC highspeed circuit design requirements, and larger IC package size trends are impacting ESD protection capability, see Chapter 2 for details. These constraints can inhibit the ESD design methodology required to meet the customer-specified 500 or 250 volt CDM levels. This is especially true for very high-speed high-performance pin design types, which have limitations in CDM discharge peak current. As a result, practical designs are restricted to 2-6 amperes of peak CDM current, which translates to a CDM target level of 125-400 volts for many advanced technology products (depending on pin-count). In the same vein, ultra-high-speed designs > 200 Gb/s in the sub-10 nm technologies can be constrained by even tighter CDM peak currents in the range of 2 to 3 amperes for non-RF I/O.

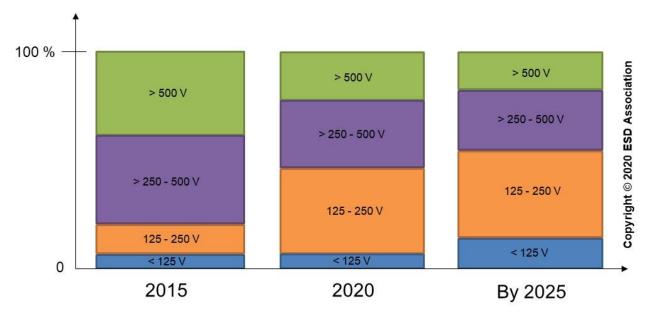

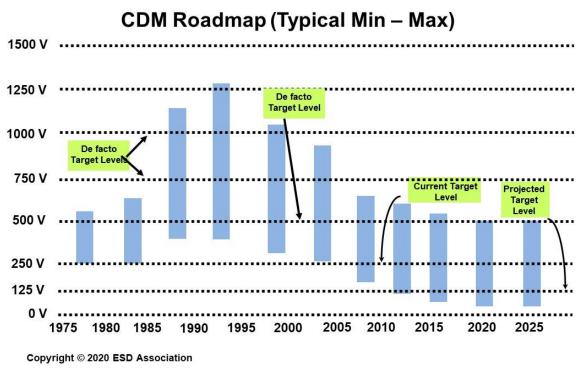

**Evolution of Perceived CDM Requirements:** 500 volts can no longer be routinely met for the reasons discussed above, often leading to delays in qualification and time-to-market. The more important focus should be that the designs can no longer support these previous levels and that with the available CDM control methods there is no need for higher CDM levels ( $\geq$  500 volts) that make the designs nearly impossible to meet circuit performance. In addition, even if only a small portion of the IC products are designed to be in the market with a high-speed interface, these high-speed interfaces now require consideration for even lower CDM targets compared to most products without these interfaces. Estimates from the ESD Association's Technology Roadmap [2] do show an expected increase in the number of products that are predicted to have CDM levels below 125 volts by 2025 as shown in Figure 1.

Figure 1: Forward-Looking Charged Device Model Sensitivity Distribution Groups

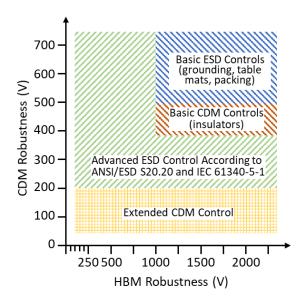

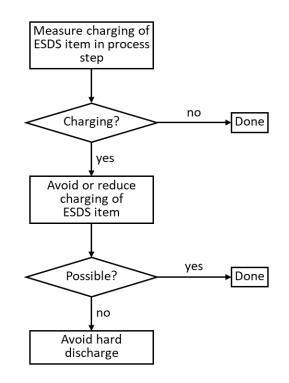

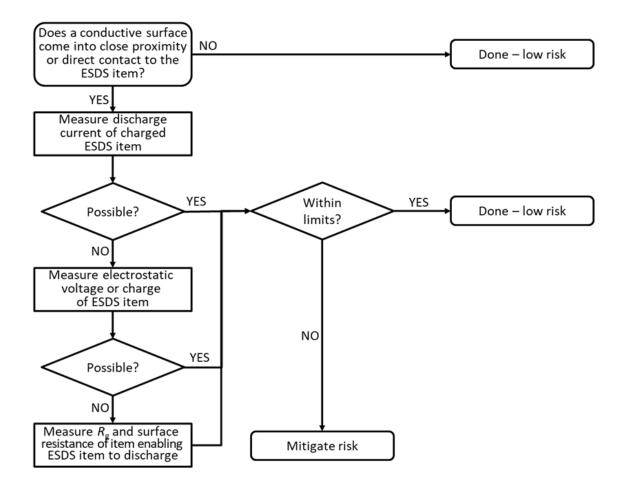

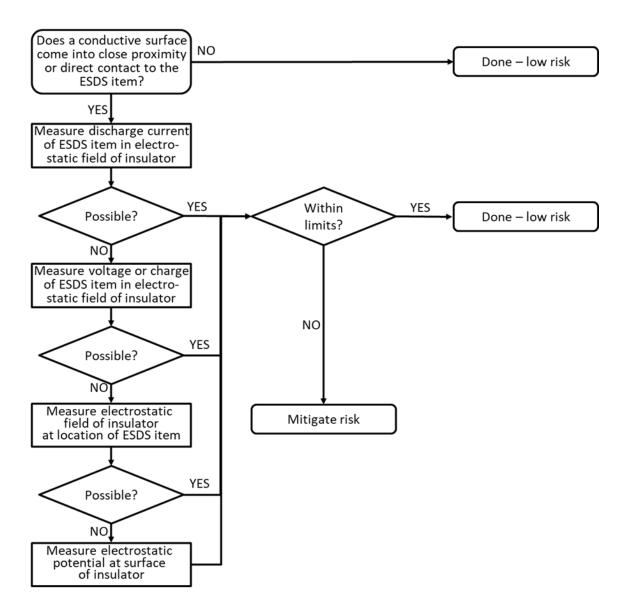

**Improved state-of-the-art CDM ESD control** methods in practice in the industry today. Basic controls allow safe handling for devices with CDM pass voltage levels as low as 200 volts and with process assessment techniques as discussed in <u>Chapter 3</u> and further in ANSI/ESD SP17.1 enabling lower levels. This work has revealed several important findings that need to be considered.

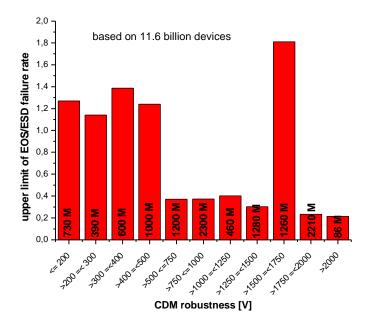

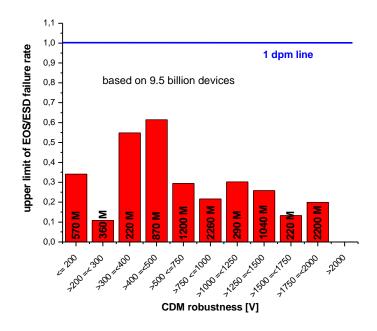

- A. Field return data from 11 billion IC devices show that customer returns can occur for products with CDM pass levels from 200 volts to 2000 volts, meaning control of CDM at production sites is more important than a specific performance target level. <u>See Chapter 4.</u>

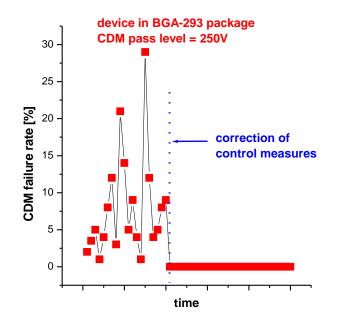

- B. Field failures also can occur when proper CDM control is not established during a product ramp-up (pre-qualification), meaning that production failures must be addressed by correcting the CDM control methods at critical process steps rather than requiring the designs to pass at higher voltages than are achievable by design. See Chapter 3.

- C. CDM control measures are available throughout the industry to meet safe manufacturing and handling of products at 200 volts or above, meaning that products designed for CDM levels at 250 volts or 500 volts can be equally safe and reliable. Process assessment techniques as discussed in <u>Chapter 3</u> and further in ANSI/ESD SP17.1 can be used to address even lower CDM target levels.

- D. Thus, any product with a CDM passing level of 250 volts or higher can be handled safely and reliably in a facility with basic CDM control measures. This level of protection should result in minimal impact on design and IC circuit performance requirements and make them compatible with current technology trends. See Chapter 5.

- E. As future IC technologies are enabled, there should be a continuous improvement of CDM control with even more advanced methods coming into practice.

- F. Recently, a standard practice document ANSI/ESD SP17.1 [3] was developed by the ESD Association introducing advanced process assessment techniques valuable for assessing risks below 200V and which can be utilized for dealing with CDM at or below 125 volts. See Chapter 3.

**<u>Recommended CDM Levels</u>**: Based on this extensive study, a safe and practical CDM passing level of 250 volts is recommended as outlined in Table I below. Products with a CDM target level lower than 250 volts should implement additional process-specific measures for CDM control, especially during product ramp-up. For products in this category, process-specific techniques, as described in ANSI/ESD SP17.1, are mandatory.

| CDM classification level<br>(tested acc. to<br>ANSI/ESDA/JEDEC<br>JS-002) | ESD Control Requirements                                                                                                                                                                                                                                                                                                                                                                |

|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $V_{CDM} \ge 200 V$                                                       | • <b>Basic ESD control methods</b> with the grounding of metallic machine parts and control of insulators according to standards like ANSI/ESD S20.20, IEC 61340-5-1, or JEDEC JESD625                                                                                                                                                                                                  |

| VCDM < 200 V                                                              | <ul> <li>Basic ESD control methods with the grounding of metallic machine parts and control of insulators +</li> <li>Process specific measures to reduce the charging of the device OR to avoid a hard discharge (high resistive material in contact with the device leads) +</li> <li>Charging/discharging measurements at critical process steps following ANSI/ESD SP17.1</li> </ul> |

Table I: Recommended CDM Classification Based on Factory CDM Control

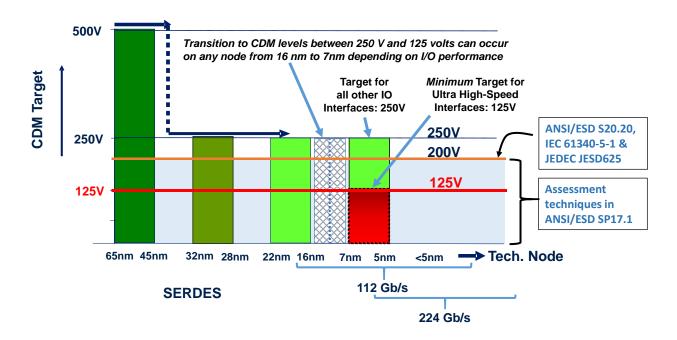

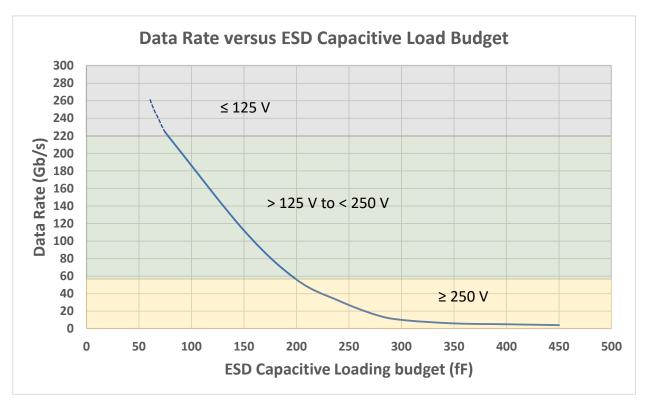

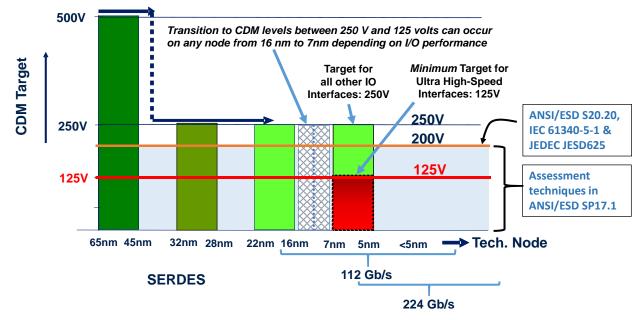

Updated Roadmap for continued silicon technology scaling. With more recent developments requiring ultra-high-speed interface designs in technologies of sub-10 nm, the CDM Roadmap has been revised as shown in Figure 2. This was driven by targets for 5 nm SoCs and beyond for operations @ 56 GHz (Nyquist) or 224 Gb/s PAM4. As designs are now limited to 75 fF of ESD loading capacitance, a target level of 125 volts has become necessary (as indicated by the red bar in the figure) for this ultra-high-speed interface. Package sizes for large ICs, such as microprocessors, at these performance levels, dictate the CDM peak discharge current. To recognize this constraint, the Industry Council is also recommending that the max target peak current of associated 224 Gb/s PAM4 high-speed IP blocks be 2.5 amperes. Advanced process assessment techniques as specified in ANSI/ESD SP17.1 can enable a path to safe manufacturing at these lower target levels. At the same time, lower performance I/Os such as standard GPIO interfaces should still be targeted at 250 volts leveraging basic control methods as described in ANSI/ESD S20.20 [4], IEC 61340-5-1 [5], and JEDEC JESD625 [6] this will help minimize the manufacturing risks on products that may have a high-performance I/O. This is explicitly shown in the figure at the 7 to 5 nm node with the green bar at 250 volts in the figure for standard I/Os, and the red bar at 125 volts for ultra-high-speed 224 Gb/s PAM4 I/O interfaces. The choice of qualification thus depends on the I/O applications.

Figure 2: Technology scaling effects on practical CDM levels and the associated CDM control requirements

As I/O performance levels increase above 56 Gb/s PAM4, a reduction in the maximum peak current design target will be needed for CDM due to reductions in the ESD design window based on technology, package size, and I/O performance. This means that even 250 volts may not be achievable and still meet performance requirements. However, care should be taken on the design side to ensure that if a target level of 250 volts cannot be met as a function of the ESD window, package size, and performance reasons, as discussed in <u>Chapter 2</u>, that the achievable target level is *maximized* to reduce manufacturing risks. The designed target level for the product must also be in line with the manufacturing capability. Simply reducing the target level directly to 125 volts may not be prudent for the manufacturing capability. It should be noted that as CDM target levels drop below 200 volts, data, as shown in <u>Chapter 4</u> is limited, and proper manufacturing ESD controls may not have been implemented yet. Care should also be taken to ensure that proper ESD controls are in place and that the proper process assessments have been made in the manufacturing flow as per ANSI/ESD SP17.1 for whatever CDM target level is achievable. This will ensure the manufacturing environment can manage the risks with component target levels moving towards 125 volts.

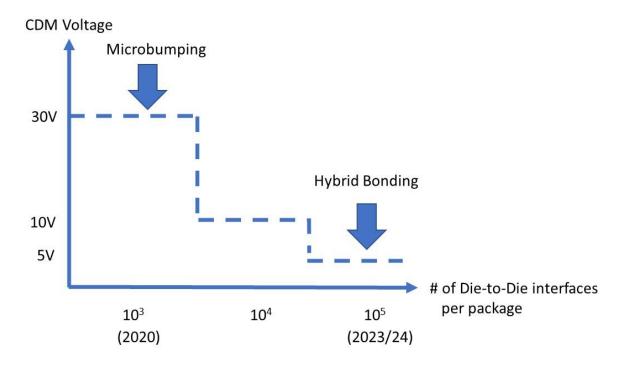

**<u>3D IC CDM Targets</u>**: As described in the GSA roadmap [7] for 3D ICs, in 2.5D and 3D packaging processes, with die stacking some micro-bumps are not connected to the external package ball, but can experience ESD exposure during a few process steps of the manufacturing process. In these packaging technologies, the number of micro-bumps can range from hundreds up to tens of thousands, a CDM target I<sub>PEAK</sub> range from 100 milliamps to 1 ampere is discussed for qualification. Careful consideration of ESD controls in a few critical process steps will guarantee the safe handling of these micro-bumps in manufacturing. The qualification can be done by assessing these internal bumps with very fast TLP (VF-TLP) or wafer-level CC-TLP equipment.

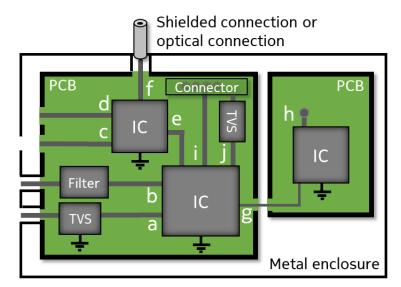

**External/Internal High-Speed I/Os:** Externally exposed high-speed I/Os require extra ESD control precautions in the handling, manufacturing, assembly, testing, and system installation phases. At the same time, internal I/O are not immune to ESD risks. <u>Appendix A</u> explains how the

risk of CDM events is limited with a product's internal I/O but can exist especially during printed circuit board (PCB) and system assembly if ESD control precautions are not fully implemented, while external I/O have extra precautions that may need to be taken to ensure these I/O are safe in real-world environments.

<u>CDM Qualification of Interface IP</u>: Determining whether an IP, when integrated into the product, is expected to pass the product's classification level is uncertain at best for the end-user. This is because the standard CDM qualification of an IP interface to a voltage class is not practical as products are qualified for a given package type or package size. For this purpose, a qualification method for IP based on a CDM peak current as a qualification parameter is suggested as guidance in <u>Appendix B</u>.

<u>Test Methods for Sensitive CDM Targets</u>: As the CDM target levels are reduced to below 250 volts, proper test methods and accuracy of the test will become critical. <u>See Appendix C</u>. Various techniques are being investigated to improve the present air discharge test method for its fidelity. At the same time, there is a much more serious effort to introduce contact-based testers for better reliability at lower CDM test voltages. It is likely a standard will be developed allowing for both air discharge and contact-based testers to be used alternatively. Currently, a method for contact based CDM testing called low-impedance contact CDM has been released as a standard practice [8]. These critical developments are concurrently taking place as CDM targets below 250 volts and as low as 125 volts are recommended.

Final Words: This revision of White Paper 2 addresses the critical need for CDM targets for ultrahigh-speed I/O interfaces operating at data rates > 200 Gb/s and establishes that a safe level of 125 volts CDM can be recommended. At very high-speed I/O interface data rates > 56 Gb/s, a combination of factors, including the ESD design window for the technology, package size, and I/O performance can drive a reduction in the designed peak current target, meaning 250 volts may not be achievable, but design efforts should focus on maximizing the achievable peak current level to minimize manufacturing risk. Various process assessment techniques (as described in ANSI/ESD SP17.1) are necessary to address the added risks in manufacturing below 200 volts. It is important to emphasize again that all products with standard, lower performance I/Os, should still target 250 volts with manufacturing using known basic control methods such as described in ANSI/ESD S20.20, IEC 61340-5-1, and JEDEC JESD625. Better IPEAK control for accuracy at lower voltages in the CDM standard test methods to validate these CDM target levels is in progress. Although not previously considered for any packaged product, interface IP qualification needs to be addressed and this can be achieved by using a recommended standard for peak current as the target. Finally, it is also recognized that exposed high-speed interface I/Os in a system need special ESD protection requirements, whether they are considered external to the system or not.

#### References

- [1] White Paper 1: "A Case for Lowering Component Level HBM/MM ESD Specifications and Requirements," June 2018, <u>http://www.esdindustrycouncil.org/ic/en/documents</u>

- [2] ESD Technology Roadmap from the ESD Association, <u>https://www.esda.org/standards/</u>

- [3] ANSI/ESD SP17.1-2020 "For the Protection of Electrostatic Discharge Susceptible Items Process Assessment Techniques", 2020 <u>http://www.esda.org/standards/esda-documents.</u>

- [4] ANSI/ESD S20.20-2014, "Development of an Electrostatic Discharge Control Program for Protection of Electrical and Electronic Parts, Assemblies and Equipment", July 2014 <u>http://www.esda.org/standards/esdadocuments.</u>

- [5] IEC 61340-5-1:2016, "Protection of Electronic Devices from Electrostatic Phenomena General Requirements", May 2016 <u>http://webstore.iec.ch</u>

- [6] JEDEC JESD625B "Requirements for Handling Electrostatic-Discharge-Sensitive (ESDS) Devices", January 2012 <u>http://www.jedec.org.</u>

- [7] Global Semiconductor Alliance, "Electrostatic Discharge (ESD) in 3D-IC Packages", Version 1.0, January 2015 http://www.gsaglobal.org/working-groups/3d-ic-packaging/.

- [8] ANSI/ESD, SP5.3.3-2018. "Low Impedance Contact CDM as an Alternative CDM Characterization Method", February 2019.

# **Table of Contents**

| Glossar    | Glossary of Terms                                                                                |      |

|------------|--------------------------------------------------------------------------------------------------|------|

| Executiv   | ve Summary                                                                                       | 8    |

| Chapter    | Chapter Summary                                                                                  |      |

| Append     | ix Summary                                                                                       | 17   |

|            | tly Asked Questions                                                                              |      |

|            | 1: CDM Background and History                                                                    |      |

| Chapter    | 2: CDM Challenges to IC Component ESD Design                                                     | 32   |

| 2.1        | Introduction                                                                                     |      |

| 2.2        | The CDM Event from the ESD Designer's Perspective                                                | 33   |

| 2.3        | Design Techniques for CDM                                                                        |      |

| 2.4        | Technology Scaling Effects on CDM ESD Robustness                                                 |      |

| 2.5        | Examples of CDM Impact on Integrated Circuit ESD Design                                          | 38   |

| 2.6        | Package Effects and Package Trends                                                               | 43   |

| 2.7        | ESD Designer's Perspective on Realistic CDM Targets                                              | 46   |

| 2.8        | Further Technology Scaling Effects and Additional Impact on Realistic CDM Targets                | 48   |

| 2.9        | High Speed/RF Circuits, Scaling Impact on CDM Targets                                            | 48   |

| Chapter    | 3: CDM Related ESD Process Assessment                                                            | 56   |

| 3.1        | Motivation                                                                                       | 56   |

| 3.2        | Basic Idea of CDM Protection and Process Related Risk Analysis                                   | 57   |

| 3.3        | Process Capability & Transition Analysis                                                         |      |

| 3.4        | Advanced Process Risk Assessment Based on ANSI/ESD SP17.1                                        | 72   |

| 3.5        | Conclusions                                                                                      | 81   |

| Chapter    | 4: Consolidated Industry Data on CDM levels vs. Field Returns                                    | 83   |

| 4.1        | Field Return Rates versus CDM Voltage Level                                                      |      |

| 4.2        | Analysis of Typical Examples                                                                     |      |

| 4.3        | Conclusions                                                                                      |      |

| Chapter    | 5: Recommendations for Realistic CDM Target Levels for the Present and an Outlook for the Future |      |

| 5.1        | Preface                                                                                          |      |

| 5.2        | Relevance of Current Level                                                                       | 88   |

| 5.3        | Relevance of Voltage Level                                                                       |      |

| 5.4        | Correlation to Control Measures in Manufacturing Environment                                     |      |

| 5.5        | Recommended CDM Target Level                                                                     |      |

| 5.6        | Outlook and CDM Roadmap from Silicon Technology Scaling                                          |      |

| 5.7        | Outlook and CDM Roadmap from Silicon Technology Scaling– Impact of 3D ICs                        |      |

| 5.8        | Challenges and Future Direction of Low Voltage CDM Testing                                       |      |

| 5.9        | Guidance for Design                                                                              |      |

| 5.10       | Summary                                                                                          |      |

|            | ix A: External Versus Internal High-Speed I/Os                                                   |      |

| A.1        | Introduction                                                                                     |      |

| A.2        | Exposed High-Speed I/Os                                                                          |      |

| A.3        | Product Internal High-speed I/Os                                                                 |      |

| A.4        | ESD Risk Classification with High-speed I/Os                                                     |      |

|            | ix B: CDM Qualification of Interface IP Based on Peak Current                                    |      |

| B.1        | Introduction                                                                                     |      |

| B.2        | Choose Target Peak Current                                                                       |      |

| B.3        | Qualification Voltage Setting from Test Chip CDM Voltage and Peak Current Relationship           |      |

| B.4        | Perform CDM Qualification Testing                                                                |      |

| B.5        | Summary                                                                                          |      |

|            | ix C: CDM Qualification and Test Methods                                                         |      |

| C.1        | CDM Qualification Standards                                                                      |      |

| C.2        | Comparison of Existing CDM Industry Standards                                                    |      |

| C.2<br>C.3 | Sources and Impact of Zap to Zap and Tester to Tester Variation                                  |      |

| C.3<br>C.4 | Emerging Test Methods                                                                            |      |

| C.4<br>C.5 | Conclusions and Outlook: CDM Test Methods                                                        |      |

|            | ix D: Some Aspects of CDM Tester Circuit Modelling                                               |      |

| D.1        | Introduction                                                                                     |      |

| $\nu$ .1   |                                                                                                  | .120 |

| D.2        | CDM Tester Model                                                     | .129 |

|------------|----------------------------------------------------------------------|------|

| D.3        | Waveform Analysis                                                    | .133 |

| D.4        | Conclusions                                                          | .137 |

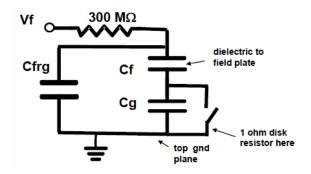

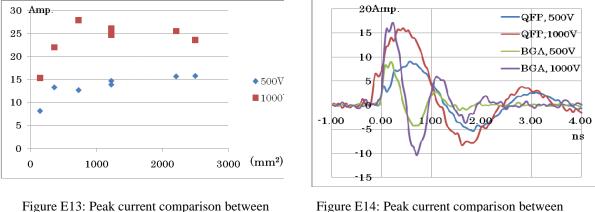

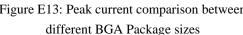

| Appendix   | E: CDM Tester Limitations in Representing Real-World Events          | .140 |

| E.1        | Physics of Real-World CDM                                            | .140 |

| E.2        | Consideration and Analysis of Real-World CDM                         | .144 |

| E.3        | Differences Between Real-World CDM and Tester World CDM              | .147 |

| E.4        | CDM Waveform Comparison Between Real World and Tester                | .148 |

| E.5        | Conclusions                                                          |      |

| Appendix   | F: CDM – Does it Correlate to Other ESD Stresses?                    | .152 |

| F.1        | Theoretical Analysis                                                 |      |

| F.2        | Example and Case Studies                                             |      |

| F.3        | Conclusions                                                          |      |

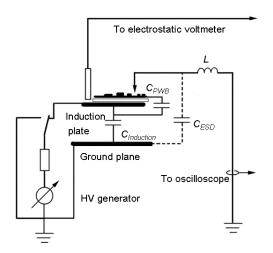

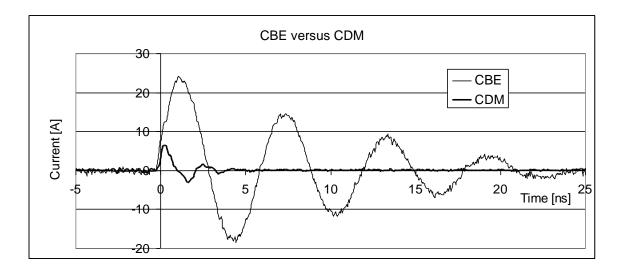

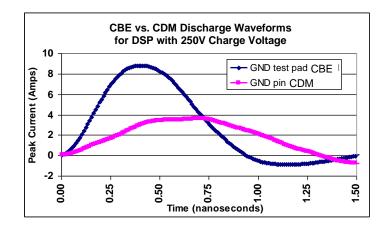

| Appendix   | G: Charged Board Events and Relationship to CDM                      | .161 |

| G.1        | Charged Board Event Problem Statement                                |      |

| G.2        | Charged Board Event (CBE) Overview                                   |      |

| G.3        | Relation of Charged Board Events to Component-level ESD Test Methods |      |

| G.4        | Charged Board and Related Failure Case Studies                       | .162 |

| G.5        | Example Charged Board Event Testing Methods                          | .163 |

| G.6        | Charged Board Event Test Results                                     | .165 |

| G.7        | Identifying and Minimizing Charged Board Event (CBE) Failures        | .167 |

| G.8        | Summary                                                              |      |

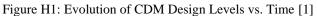

| Appendix   | H: Impact of CDM Requirements on Products                            |      |

| H.1        | CDM ESD Requirements                                                 |      |

| H.2        | Impact of Goals on Products                                          |      |

| H.3        | Supplier / Customer Impact of a Revision to the CDM Target Levels    |      |

| Revision l | History                                                              | .173 |

# **Chapter Summary**

<u>Chapter 1:</u> History of charged device model since the initial 1974 publication is reviewed and major developments, mostly concerning CDM testers, are noted chronologically. No significant changes have been made since the 2010 release, minor updates, and realignment only.

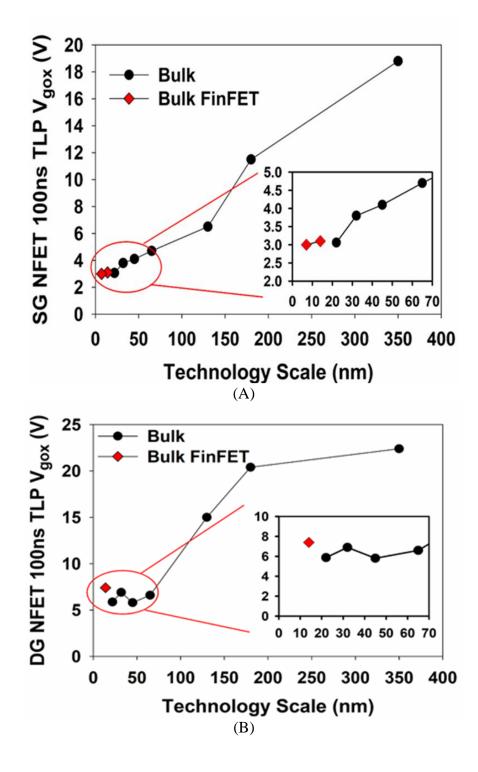

<u>Chapter 2:</u> This chapter outlines the protection design limitations associated with silicon technology scaling and the demand for high-speed circuit performance. These protection design limitations become more pronounced with the trend for larger area, high pin count packages. With these constraints in view, the chapter points out the realistic CDM target levels that can be achieved in design today. These limits are recommended for two different applications: general I/O applications versus high-speed applications. Significant changes have been made to this chapter since the 2010 release, many figures have been updated with recent trends and Section 2.9 added.

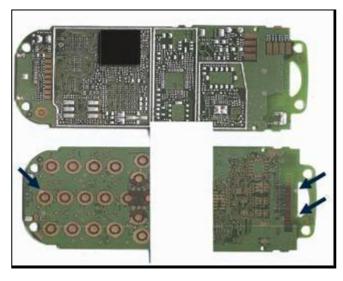

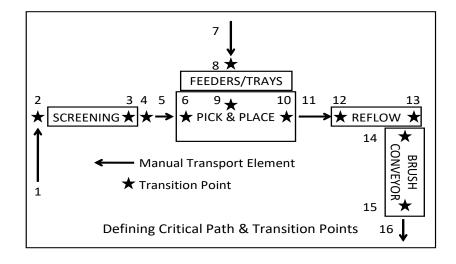

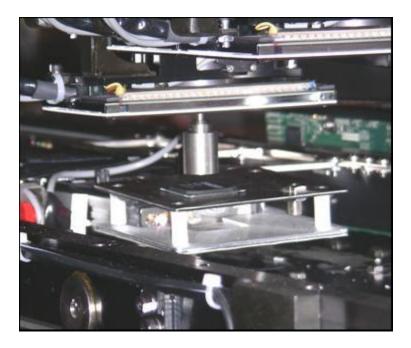

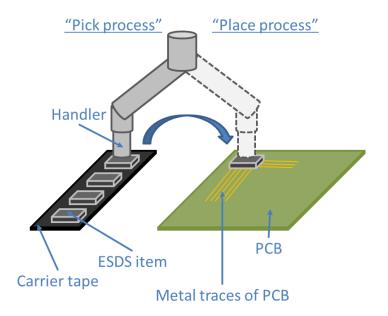

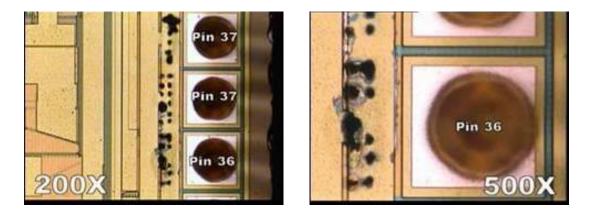

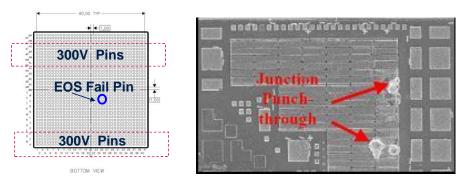

<u>Chapter 3:</u> The chapter describes two similar methods to analyze an assembly area for CDM risk and explains how to use these methods in actual production lines with examples. The field problems presented also show that if such a CDM risk analysis is not performed, even devices considered CDM robust may fail during assembly or testing since the board can get charged and discharges with a higher discharge current than a single device at the same voltage level. A risk analysis performed following the described methodologies enables the manufacturer to handle even very CDM sensitive devices. Significant changes have been made since the 2010 release with the overall chapter updated to introduce techniques discussed in ANSI/ESD SP17.1 and new examples added.

<u>Chapter 4</u>: The field return data of 11 billion shipped parts consolidated from numerous IC manufacturers are analyzed. The device types range from discretes to ULSI system-on-chip parts. Primarily field returns from the board manufacturers and end-customers have been considered. There is a weak dependence on the combined EOS and ESD failure return rate on the CDM qualification level. In a data subset of 1.5 billion parts, it is demonstrated that EOS-related fails (not CDM-related fails) are dominating the failure statistics. Typical examples confirm that CDM-related returns are usually caused by problems in the ramp-up phase of a manufacturing process. Minor yet critical changes in the ESD control of the manufacturing process solve these problems immediately as shown in Chapter 3. No significant changes have been made since the 2010 release, minor updates, and realignment only.

<u>Chapter 5:</u> This chapter presents a total perspective on CDM control techniques available for production areas and based on this, recommends a realistic yet safe categorization of target levels that are linked to the required degree of CDM control methods. Considering all aspects from design capability to field reliability and combined with the currently practiced CDM control methods, it is proposed that a CDM level of 250 volts is a safe qualification level for the vast majority of integrated circuits in manufacture today. ICs with ultra-high-speed interface pins (> 200 Gb/s) require a qualification level of 125 volts due to design constraints. As the electronics industry progresses to even higher performance products and technologies it is expected that the proportion of products requiring CDM levels below 250 volts will increase. Consequently, continuously improved and monitored CDM control at the production areas must become a routine practice. Significant changes made since the 2010 release, updating and adding many sections as well as outlook and roadmap to align with today's technology trends for high-speed IOs.

# **Appendix Summary**

<u>Appendix A:</u> This appendix discusses how to classify high-speed I/Os as internal or external based on the accessibility during various processing and handling phases. This helps to estimate what type of I/Os have a higher probability to be exposed to ESD stress during processing, installation, and use. This is a new appendix introduced with this release of the white paper.

<u>Appendix B</u>: This appendix addresses how the specific nature of CDM demands a dedicated methodology to assess the CDM robustness of sub-circuits, like interface IP, and describes a proposal for an appropriate CDM qualification method for these IPs. In order to enable a valid assessment of the CDM robustness that holds equally for both test chip and product, the CDM discharge peak current is proposed as a measure of the CDM robustness, instead of the voltage. This is a new appendix introduced with this release of the white paper.

<u>Appendix C:</u> This appendix describes existing CDM ESD test methods and standards and summarizes the differences between them. The challenges of air discharge testing are discussed, especially for low voltage testing. New test methods, which show great promise for extending reliable CDM testing to lower stress levels, are introduced. This is a significant rewrite of the appendix since the 2010 release to align with the state of CDM test standards today.

<u>Appendix D</u>: Simple circuit models can explain the major features of charged device model (CDM) non-socketed ESD testers as specified in the ANSI/ESDA/JEDEC JS-002-2018 CDM standard. A simple lumped series LRC model is estimated, and it explains features observable up to 1-2 GHz. This includes all major trends for peak current (I<sub>PEAK</sub>), which is plotted in the plane of effective L and C for a given value of spark resistance R. Extensions of this basic circuit model to a distributed one explain many reported high-frequency CDM effects. No significant changes have been made since the 2010 release, minor updates, and realignment only.

<u>Appendix E:</u> A comparison between the CDM events in the real world and those in the tester world is presented along with descriptions of some typical cases. This appendix shows that the peak CDM discharge current from a high capacitance device in the real world is typically not as high as that in the tester world except on a power pin (bus). No significant changes have been made since the 2010 release, minor updates, and realignment only.

<u>Appendix F</u>: It is shown that no correlation of CDM to any other stress types (e.g. HBM, EOS, and CBE) can be expected. Therefore, CDM cannot be replaced by, nor replaces, any of the other stress types. Consequently, a reduction in CDM target levels should not lead to a lower performance for other stress types. No significant changes have been made since the 2010 release, minor updates, and realignment only.

<u>Appendix G</u>: This appendix outlines charged board events (CBE) that result in damage to IC devices placed on printed circuit boards. The various charge/discharge mechanisms are described. Charged board events are higher energy counterparts to CDM for IC components, but different IC failure mechanisms result which do not correlate to other ESD event methods. A literature review is given along with techniques to evaluate CBE on systems. Recommendations to reduce CBE impact include improved ESD control and circuit board design/implementation guidelines. No significant changes have been made since the 2010 release, minor updates, and realignment only.

<u>Appendix H:</u> A review of the current CDM goals for IC's from a manufacturer and customer view and the impacts that the current goals have on the manufacturer and end customer. The costs to the manufacturer of the current CDM target levels are highlighted in terms of design revision and time to market delay; the benefits of a new target level are similarly highlighted. This appendix was the previous Chapter 4 in the 2010 release (moved to Appendix H in this revision of the white paper) and has been updated with an updated roadmap and minor updates since the 2010 release.

# **Frequently Asked Questions**

#### FAQ on CDM Qualification

#### Q1: Customers did not specify CDM levels before. Why are they asking for it now?

Answer: As the importance of HBM diminishes (even for units shipped below specification levels) as demonstrated by a lack of field returns, customers are focusing more on CDM-based field failure signatures, which are distinct from HBM.

*Q2:* If CDM methodology and levels are modified would there be more fallout for EOS at the component or System Level?

Answer: CDM and EOS failures are completely different in total energy and time duration. Effective CDM protection does not guarantee EOS protection. EOS protection must be provided at the system level. There is no correlation between component CDM failures and system EOS failures. The fallout rate due to EOS would not change as a result of modifying CDM methodology and levels.

# Q3: As products with low CDM values have an increased risk for problems at introduction, shouldn't we aim for larger CDM levels?

Answer: Where a target level of 250 volts can be achieved in design without degrading electrical performance or incurring additional product cost, this level of CDM should continue to be implemented. However, <u>Chapter 2</u> clearly shows that for several applications even 250 volts may not be feasible. <u>Chapter 3</u> shows that solving the problems by CDM control measures is much more efficient than increasing the CDM robustness level at the cost of functional performance.

#### Q4: How is it determined that CDM levels lower than 500 volts are safe?

Answer: It has been proven that even 200 volt CDM can safely be manufactured if appropriate CDM control measures are taken (see <u>Chapter 3</u>). The assessment of ESD control measures and the field return data show that devices with 250 volts are equally as safe as 500-volt CDM parts in typical modern manufacturing sites.

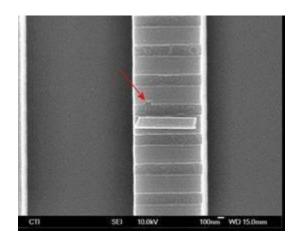

#### Q5: When and where do classic CDM failures happen?

Answer: The classic CDM failure mechanism is a dielectric breakdown failure signature happening mainly in the ramp-up phase of a new product in the test area for a semiconductor manufacturer. This can also happen in PCB assembly lines or system assembly lines especially when new process steps are introduced.

*Q6:* If the specifications are meant for all pins on a package, would it not make more sense to require higher levels for the corner pins?

Answer: With the automated pick and place tools today, any of the pins could make first contact. All of the pins need to be considered, the corner pins should not be treated any differently.

#### *Q7:* The council made a case about lowering HBM levels. Will CDM levels follow automatically?

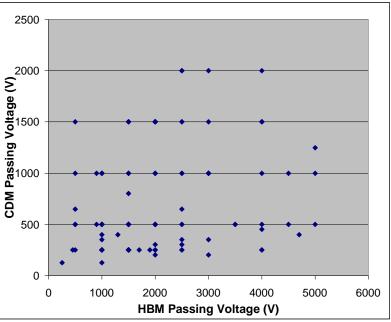

Answer: It has been shown that the HBM and CDM fail levels are largely uncorrelated. This is demonstrated in <u>Appendix F, Section F.2</u>. This is mainly due to the completely different physical discharge mechanisms and failure modes between the two models.

#### *Q8:* Should CDM qualification levels be uniform for different I/O interfaces?

Answer: Naturally one would assume that the CDM target would be independent of I/O interfaces. However, for high-speed applications above 56 Gb/s, target levels below 250 volts may be necessary depending on the package size, I/O performance, and technology but not necessarily stepping directly to 125 volts, as discussed in this document. Simply reducing the target level directly to 125 volts may not be prudent for the manufacturing capability. Care should be taken to ensure that proper ESD controls are in place and that the proper process assessments have been made in the manufacturing flow as per ANSI/ESD SP17.1 for whatever CDM target level is achievable. However, lower performance I/O interfaces than mentioned above should still be targeting 250 volts to minimize manufacturing risks.

#### *Q9:* Are the CDM target levels for all interfaces with a data rate above 56 Gb/s lowered?

Answer: The lowering of the CDM target levels is driven by the need of exploiting the high-speed performance per lane. Any interface where the speed <u>per lane</u> exceeds 56 Gb/s can apply a reduction below 250 volts. How far below 250 volts the target level needs to go is a function of how far the performance is pushed above 56 Gb/s. <u>See Chapter 2</u>.

#### FAQ on CDM Control

*Q10:* If the production areas have basic controls for ESD would these methods also provide the necessary protection for CDM?

Answer: If basic ESD controls as defined in ANSI/ESD S20.20 or equivalent are used, production areas should be able to handle CDM target levels of 250 volts – this has been proven out over the past 10+ years since the release of this white paper in 2009. As targets levels are reduced to levels below 200 volts CDM, care should be taken to minimize the number of pins being reduced to these lower levels as more advanced process assessment techniques such as those called out in ANSI/ESD SP17.1 may need to be employed to assess the risk in the production area. Not every production area is ready to handle target levels below 200 volts today.

Q11: Many products that have been shipped at CDM levels of 250 volts or even 125 volts seem to be safe. Is it fair to say that CDM is well controlled with the basic methods or do they need special care for the 125-250 volt range?

Answer: Basic ESD controls, including the control of insulators and E-fields, as called out in ANSI/ESD S20.20, IEC 61340-5-1, and JEDEC JESD625 should be able to handle 250-volt sensitive devices. Following the above controls and using assessment techniques as called out in ANSI/ESD SP17.1 can enable manufacturing to manage devices with sensitivity levels even in the 125-volt range.

#### Q12: What are the main weak points for CDM ESD control in manufacturing?

Answer: In contrast to controls for HBM, ESD controls for CDM rely on controlling the charge on insulators and controlling the discharge to the conductors of the manufactured devices. Chapter  $\underline{3}$  gives more detailed information.

Q13: Defining a maximum current level as a CDM target seems to be a good solution for the challenges with the design of CDM ESD protection and also a good way to overcome the issues with variations in stress between different CDM testers and different CDM testing standards. However, how does a current level as the CDM target translate into a sensitivity level that is meaningful for the manufacturing environment?

Answer: While peak current makes sense from a device design point of view, the industry views sensitivity in terms of voltage. The experience both in the ESD control field and the qualification of devices is based on voltage values of the long-standing standards. Changing this to current would confuse both the end customer and contract manufacturers. The translation from the voltage level to current stays with the ESD protection designer. Knowing the product portfolio and typical packages, an estimate of the required withstand peak current can be made (see <u>Chapter 2</u>).

### FAQ on CDM Requirements

Q14: Although your target level recommendations seem to be valid from your analysis and the collected data, our customers are not yet confident that our subcontractors have the measures to match the new requirements. How do we proceed?

Answer: By simply staying at the old levels, we will not address the design challenges which are discussed in <u>Chapter 2</u>. Additionally, the Industry Council believes that customer demands for improved I/O performance will only increase in the future, putting even more stress on the ability to achieve the current CDM target levels. Efforts to improve CDM protection in our manufacturing facilities must continue to be a focus area if we are to be prepared for these future challenges. As discussed in <u>Chapter 3</u>, basic CDM protection measures are implemented when the international standards are followed. The issue is that many are not aware of this as they do not perceive these measures as CDM protection lines with the methods as described in <u>Chapter 3</u> should be completed. This is especially true during the introduction of new process steps and during the production ramp-up phase as it has been found that CDM failures can occur for products with even higher CDM passing levels.

*Q15:* <u>Chapter 1</u> covers highlights of CDM from the US and Europe but does not mention the Far East. Weren't there some significant developments in Japan in the same time frame?

Answer: Yes, there were significant developments, and the authoritative summary is given as part of this White Paper. The essentials are as follows:

1. The first CDM paper in Japan was presented at the Electronics and Communication Conference with the title "Proposal of Charged Package Method", which influenced EIAJ Test Method IC121, Technical notes in 1988. Related EOS/ESD Symposium presentations from Japan were given in 1986, 1990, and 1992.

- 2. The EIAJ Semiconductor Reliability Sub-committee began standardizing CDM test methods in 1990; the Tentative CDM Test Method, EDX4702-01 was established in 1994.

- 3. The JEDEC Semiconductor Reliability Sub-committee (succeeding EIAJ Semiconductor Reliability Sub-committee) adopted EIAJ ED4701/300-2 (JEITA Standard) in April 2006, aligning approximately with JEDEC JESD22-C101D. The committee is now examining differences among the CDM specs and is looking for further improvements.

#### Q16: With the roadmap shown for CDM, will there be a corresponding roadmap for HBM?

Answer: HBM levels are not package dependent, and sufficient ESD controls exist in manufacturing to achieve 500 volts HBM today, so a roadmap for further reducing HBM levels is less necessary. This is explained in <u>Chapter 2</u>. Also, with today's modern packages with high pin counts, the HBM pin combination stress scenario in the real world is less meaningful. Therefore, CDM trends will be the most important and will dominate the achievable ESD levels.

#### FAQ on CDM Design

Q17: Why is the technology scaling such a severe issue for CDM design? If it is only related to gate oxide breakdown voltage limits, shouldn't the technology development engineers make the process more robust, since otherwise the transistors might get damaged during routine signal applications?

Answer: The gate oxide scaling continues for improved transistor performance. But it is about to reach a limit of tunneling effects and consequently, the actual transistors are not easily damaged under normal circuit operating voltage conditions, which also scale. However, CDM stress does not scale and gets worse for larger devices, and the breakdown voltage condition/charge trapping effects continue to take place at lower voltages. This results in major challenges for CDM protection design.

*Q18:* Why are designs facing such severe restrictions for CDM as opposed to HBM? Do you not use the same protection concepts?

Answer: While HBM designs also face restrictions as described in White Paper 1, the impact on CDM is much harsher because of the relatively higher current levels involved in this stress test at levels close to spec targets. As a result, secondary stage protection is needed for additional voltage drops. But this secondary stage results in a drastic reduction in the high-speed circuit performance and therefore CDM design is a bigger challenge. The details are presented in <u>Chapter 2</u>.

# *Q19:* If the design is such a critical issue for CDM performance is there an effort to develop more advanced protection concepts?

Answer: What we learned is that no matter which design is implemented, the fundamental nature of the capacitive loading, and its impact on circuit speeds does not change much. Some might claim that they have a more sophisticated design but eventually, the physics of the limitations would take over.

*Q20:* Would the technology shrinks and the package size increases ever come to a saturation point such that a minimum CDM target would level off?

Answer: They could and most likely would. That is why we project a minimum CDM level of 50 volts could always be designed but this would depend on the eventual trends for circuit speed performance.

*Q21:* What are the driving factors behind reducing CDM levels from 250 volts for high-speed IOs?

Answer: Several factors are driving the CDM reduction. First, the increasing package size driving increased CDM peak currents. Technology scaling, which drives reductions in the ESD design window (as discussed in <u>Chapter 2</u>), and finally, high speed/RF frequencies are increasing rapidly requiring lower ESD device capacitance values. As is noted though, this need for a reduction to a target level below 250 volts applies to very high-speed IOs (> 56 Gb/s). Lower performance IO, such as general-purpose IO, must still be designed for 250 volts as today's manufacturing is not yet ready for all pins to be below 200 volts.

## FAQ on CDM FAR

*Q22:* You claim in <u>Chapter 4</u> that a CDM testing level of >1000 volt cannot reliably be tested. Why do you include >1000-volt numbers in the analysis of <u>Appendix F</u>?

Answer: First of all, some product datasheets state > 1000-volt performance. This is because the product sustained >1000-volt discharge. Appendix F details that such stress is not always more severe than stress at a lower level. Secondly, <u>Chapter 4</u> clearly shows that at those levels no dependence on the CDM level is observed. This supports the earlier remark.

Q23: Why did you choose to remove products with more than 100 fails?

Answer: The analysis of the FARs revealed that the statistics were dominated in all voltage classes by just a few designs showing EOS failure signatures. Therefore, these outliers have been removed to show that without them there is a relatively equal distribution across all classes with a failure rate below 1 DPM.

*Q24: Is the connection between the return rate and failure rate known for the studied population? Often, the customer does not return all failures and/or does not divulge the actual failure rates*

Answer: Failure rate and return rate might not be equivalent in general. Typically, the number of fails that get returned to the IC supplier is very high for automotive applications, while for consumer ICs customers there may not be as much interest in clarifying each fail. However, as also found in White Paper 1, the statistics of both consumer and automotive parts follow the same trend.

#### FAQ on CDM Test Methods

# Q25: For CDM, is there a difference in the waveforms for inputs versus supply pins? Does this have an impact on qualification?

Answer: The CDM waveform is dominated by the capacitance between the device under test and the field plate. The total charge in the stress current is determined by this capacitance and is independent of the type of pin being stressed. Some differences in the waveform will occur due to differences in the impedance between inputs and supply pins. Comparisons of pulse shapes between ground, power, and input pins on specific examples show that input pins have a slightly lower peak current and a slightly wider pulse width. The amount of peak reduction will vary from design to design. This difference in peak current and pulse width is not a concern in qualification. Real-world CDM events will be modified by the impedance of the stressed pin in the same way as in the CDM test.

#### *Q26: How will the CDM tester variations be addressed?*

Answer: The standards bodies are always reviewing the standards to improve them. The data presented in this white paper will provide these organizations with considerable data to aid them in improving the standards. However, the standards bodies are encouraged to proceed with caution. The industry has considerable experience with today's test methods which gives users of the data a degree of confidence in the meaning of a particular pass or failure level. It is likely that any change in the standards to reduce variations will also produce a discontinuity in the measured CDM robustness levels. The standards bodies will therefore proceed with improvements cautiously.

#### Q27: Will the Industry Council address the Standards and tester variations in the future?

Answer: No. As stated previously, the Industry Council is not a standards body. We have set the recommended target levels based on the existing standards. Standard bodies have the responsibility to define physically consistent and practical standards. Test equipment vendors have the responsibility to produce testers that comply with the standards. Our conclusions in this document do not change any of these responsibilities.

# Q28: Our Company is just starting CDM testing. Which CDM standard should we use for qualification and why?

Answer: This question has become much easier in the last few years. The ANSI/ESDA/JEDEC JS-002 CDM test standard has replaced the separate JEDEC and ESDA CDM test methods. Additionally, the Automotive Electronics Council (AEC) now uses ANSI/ESDA/JEDEC JS-002 as the base document for both its CDM standards, AEC - Q100-011 Rev-D for integrated circuits and AEC - Q101-005 - REV-A for discrete components. ANSI/ESDA/JEDEC JS-002 has therefore become the default CDM test method for most products other than automotive. For automotive products, the AEC documents have some additional requirements, but the CDM tester is identical. Products sold in Japan may require the use of the JEITA CDM test method, EIAJ ED-4701/300-2 Test Method 305. It is important to remember that all of these standards address the same failure issues.

*Q29:* If our company has a 500-volt CDM part with the ANSI/ESDA/JEDEC JS-002 test method, what does this mean for the JEITA method?

Answer: A 500 volt CDM part using ANSI/ESDA/JEDEC JS-002 will likely pass at a higher voltage with the JEITA test due to the lower currents in the JEITA standard for the same voltage. It is not possible to strictly scale the passing voltage between the two test methods.

Q30: Why are there two different CDM standards? Is there a customer perception of a differing performance of one model over another? Which features of the CDM environment require three different standards?

Answer: The existence of two CDM standards, ANSI/ESDA/JEDEC JS-002 and JEITA is largely due to the different organizational structures and history and not due to an effort to model a different physical mechanism. Some people indeed prefer one standard over another. It may be due to a preference for one calibration method over another or a preference over how one standard explains the measurement procedure. Often it is due to familiarity. The use of a particular test method for an extended time will bring a level of confidence in the results. A change to a different test method will require a rebuilding of confidence.

# *Q31:* If the IC device fails CDM due to charge/rapid discharge, shouldn't the charge on the device be included in a CDM metric?

Answer: Charge is certainly an important quantity in the CDM test method. The CDM test method, however, is built on the assumption that different integrated circuits will charge to similar voltages if handled in the same way, without regard to the size of the integrated circuit. The amount of charge needed to reach a particular voltage will scale with the capacitance of the circuit to its surroundings. If the capacitance of the device to the field plate is known, it is then straightforward to calculate the charge on the device. This charge will relate to the size of the current pulse and therefore has a bearing on the protection design required for a particular size device.

### FAQ on Charged Board Events and EOS

# Q32: Are charged board events (CBE) related to CDM and hence the IC pins should be designed to CBE?

Answer: The CBE discharge mechanism is conceptually related to CDM for a single component. However, the board level aspect of CBE (much greater capacitance of supply/ground planes and reduced inductance of the supply/ground path) makes the CBE failures much more severe in comparison with CDM. They are easily mistaken for EOS. Component IC pin ESD protection cannot be designed to protect against CBE, which can be quite large and can vary considerably from application to application. Additional system-level EOS protection must be provided. See <u>Appendix G</u>.

# *Q33:* If CDM methodology and levels are modified would there be more fallout for EOS at the component or System Level?

Answer: CDM and EOS failures are completely different in total energy and time duration. Effective CDM protection does not guarantee EOS protection. EOS protection must be provided

at the system level. There is no correlation between component CDM failures and system EOS damage. Please refer to <u>Appendix F.1</u> and <u>Appendix F.1.3</u> for details. The fallout rate due to EOS would not change as a result of modifying CDM methodology and levels.

#### *Q34:* Can CDM replace or be replaced by any of the other ESD standards?

Answer: No. The energy, time duration, and nature of the discharge are so different that CDM is complementary to the other standards. <u>Appendix F</u> addresses this question.

# *Q35:* I often hear that the IEC61000-4-2 pulse is a superposition of a CDM and an HBM pulse. Can IEC 61000-4-2 ESD testing replace CDM and HBM testing?

Answer: No. Looking at the two peaks in an IEC 61000-4-2 pulse the time duration is indeed comparable to a CDM and HBM pulse. However, the required levels and discharge nature are completely different. This is because CDM is intended for component-level testing and the IEC 61000-4-2 standard is intended for system-level testing. See <u>Appendix F</u>, Sections F.1 and F.1.2. for details.

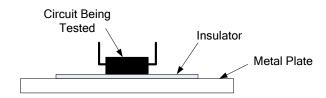

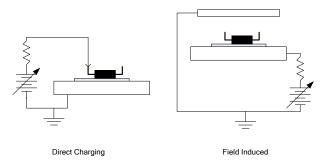

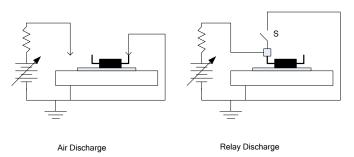

### FAQ on CDM Phenomena

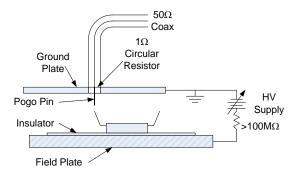

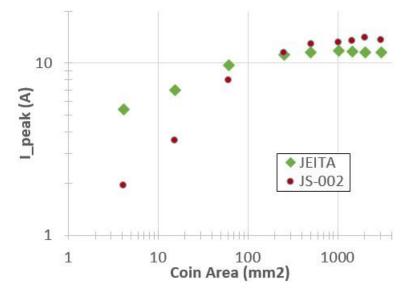

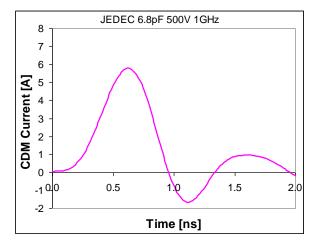

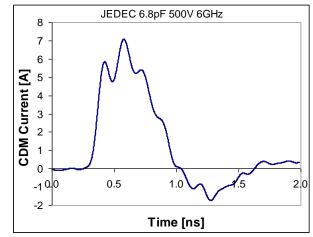

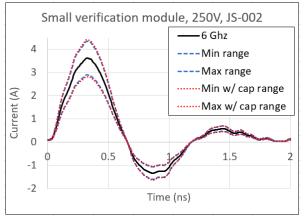

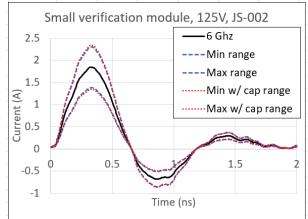

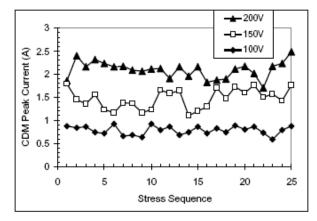

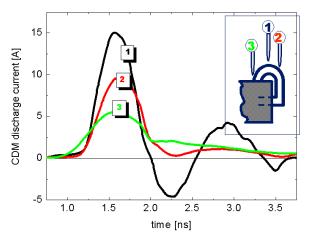

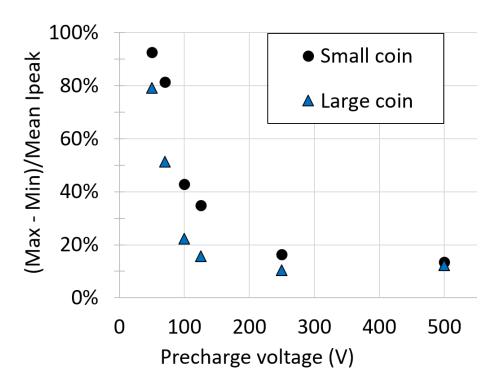

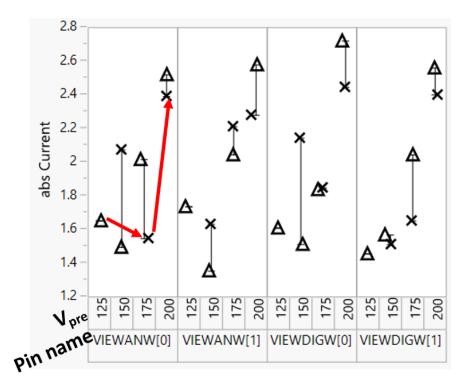

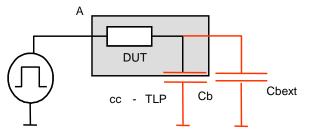

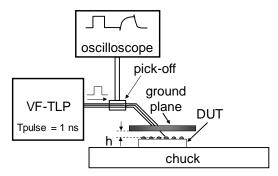

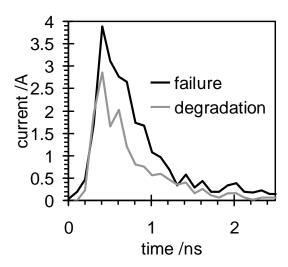

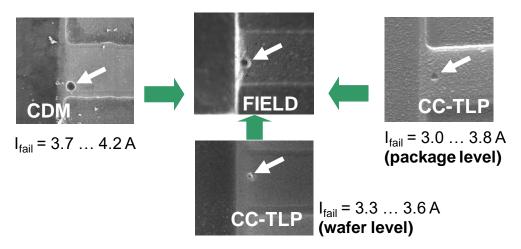

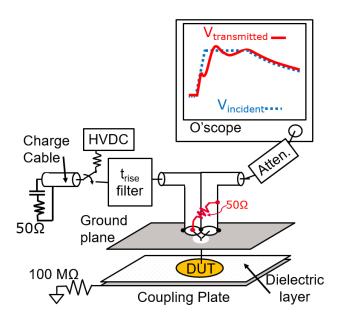

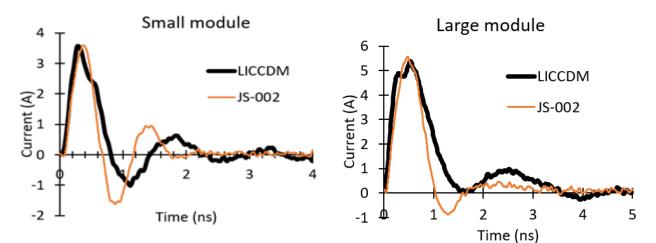

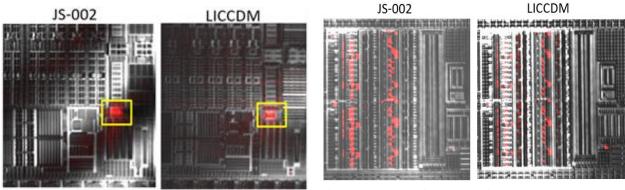

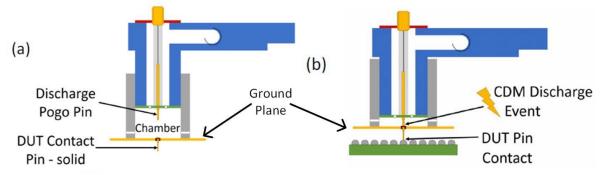

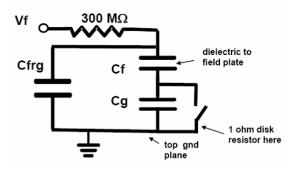

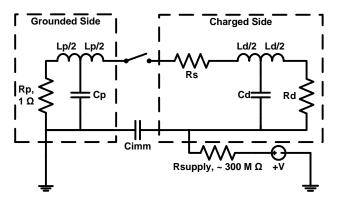

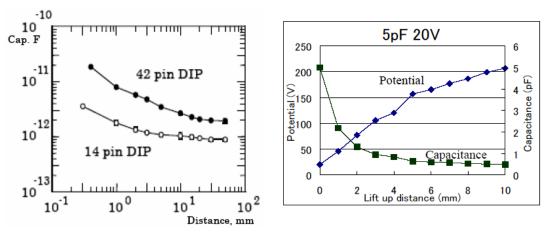

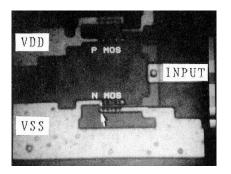

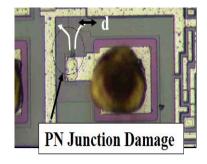

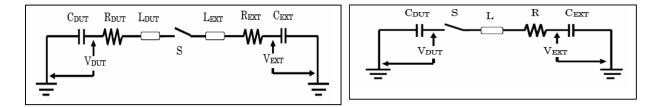

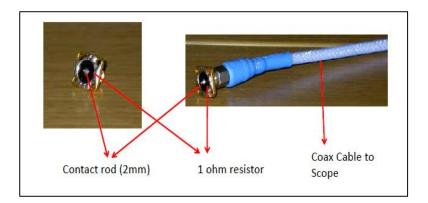

#### *Q36:* How does CDM discharge occur in the real world or the factory?